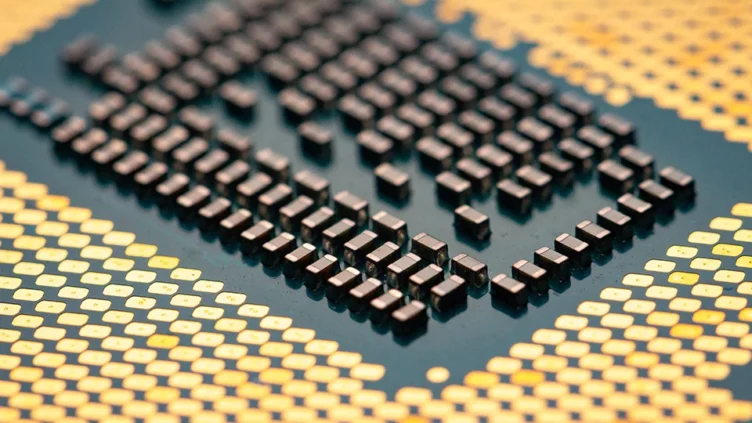

TSMC ha revelado su hoja de ruta en torno al nuevo proceso de fabricación N2 de 2 nanómetros que tiene previsto estrenar en 2025. La compañía taiwanesa ha explicado al respecto que este nodo será el primero en el que implemente la tecnología GAAFET en lugar de FinFET, que es la que emplea actualmente.

GAAFET utiliza transistores que generan una menor corriente de fuga, presentan una mayor densidad por unidad de superficie y ofrecen la posibilidad de ajustar la anchura del canal para incrementar el rendimiento o reducir el consumo.

TSMC ha indicado que esta tecnología mejorará las prestaciones por transistor entre un 10% y un 15% y reducirá el consumo entre un 25% y un 30%. Además, permitirá que la densidad de transistores aumente en más de un 15% en relación al proceso N3E de 3 nanómetros que estrenó recientemente y que está utilizando actualmente en la fabricación de los chips A17 de Apple.

Así mismo, ha confirmado que tiene previsto que la producción a gran escala de circuitos integrados fabricados con el nodo de 2 nanómetros comience a finales de 2025. También ha señalado que, en los ensayos que está realizando en sus laboratorios, está obteniendo un rendimiento que se sitúa por encima del 80% respecto a las especificaciones finales que espera obtener cuando finalice su diseño, y que el ratio de chips creados con este proceso que no presentan fallos se sitúa ya por encima del 50%.

Finalmente, TSMC ha dado a conocer que está desarrollando otro proceso llamado N2X que se empleará en la fabricación de chips de alto rendimiento que precisan de frecuencias de reloj y voltajes más elevados, aunque no ha esbozado las ventajas específicas que aportará este nodo ni cuándo espera tenerlo listo.

FOTOGRAFÍA: RYAN

El roguelike Dark Light: Survivor, anunciado para PC

El roguelike Dark Light: Survivor, anunciado para PC Hunt: Showdown 1896 llega el 15 de agosto a la PS5, Xbox Series y PC

Hunt: Showdown 1896 llega el 15 de agosto a la PS5, Xbox Series y PC El estreno de S.T.A.L.K.E.R. 2: Heart of Chornobyl se pospone hasta noviembre

El estreno de S.T.A.L.K.E.R. 2: Heart of Chornobyl se pospone hasta noviembre La versión web de Apple Maps, disponible desde hoy en beta

La versión web de Apple Maps, disponible desde hoy en beta